CY7C133

Overview

- True dual-ported memory cells which allow simultaneous reads of the same memory location

- 2K x 16 organization

- 0.65-micron CMOS for optimum speed/power

- High-speed access: 25/35/55 ns

- Low operating power: ICC = 150 mA (typ.)

- Fully asynchronous operation

- Master CY7C133 expands data bus width to 32 bits or more using slave CY7C143

- BUSY output flag on CY7C133; BUSY input flag on CY7C143

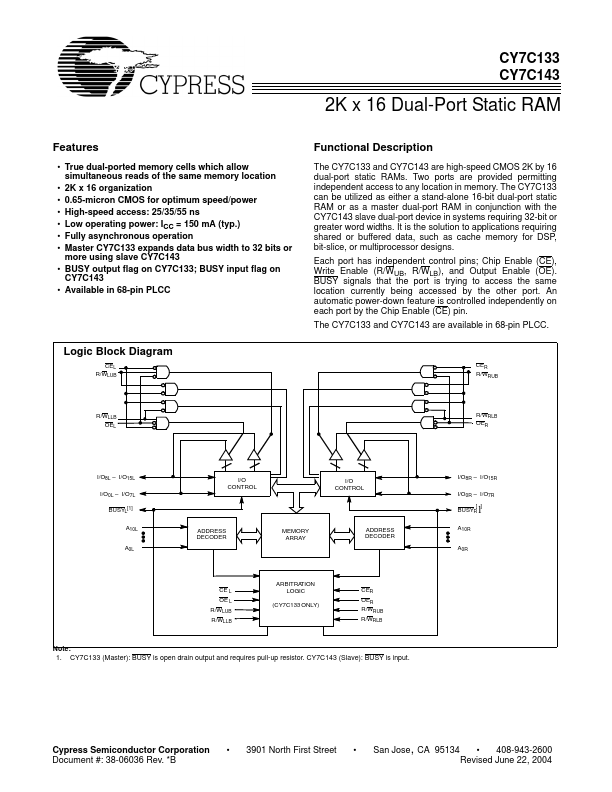

- Available in 68-pin PLCC Functional Description The CY7C133 and CY7C143 are high-speed CMOS 2K by 16 dual-port static RAMs. Two ports are provided permitting independent access to any location in memory. The CY7C133 can be utilized as either a stand-alone 16-bit dual-port static RAM or as a master dual-port RAM in conjunction with the CY7C143 slave dual-port device in systems requiring 32-bit or greater word widths. It is the solution to applications requiring shared or buffered data, such as cache memory for DSP, bit-slice, or multiprocessor designs. Each port has independent control pins; Chip Enable (CE), Write Enable (R/WUB, R/WLB), and Output Enable (OE). BUSY signals that the port is trying to access the same location currently being accessed by the other port. An automatic power-down feature is controlled independently on each port by the Chip Enable (CE) pin. The CY7C133 and CY7C143 are available in 68-pin PLCC. Logic Block Diagram